一、核心导通条件:VGS与阈值电压的博弈

NMOS(N沟道增强型场效应管)的根本导通条件是栅源电压VGS必须超过阈值电压Vth。这一关系看似简单,实则蕴含深刻的半导体物理机制与工程实践考量。

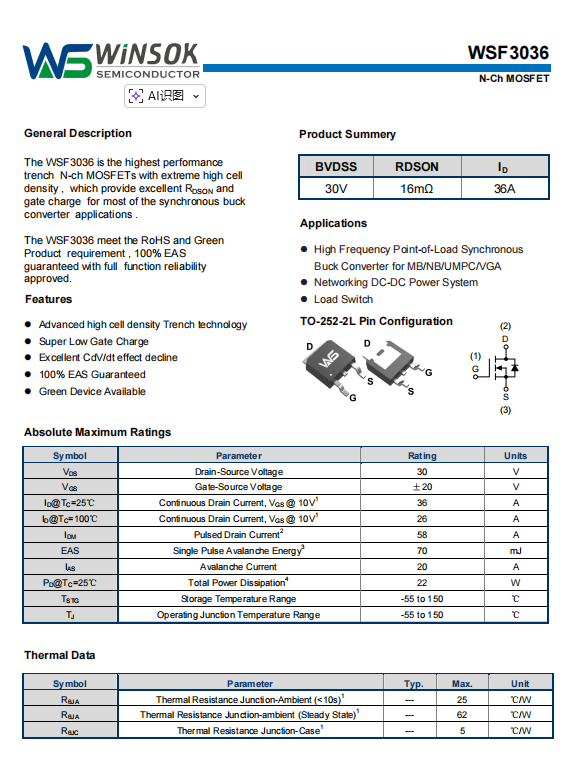

基本判据:对于N沟道增强型MOS管,当满足VGS > Vth时,器件开始导通。其中Vth典型值为2-4V(车规级器件在-40℃至150℃范围内,Vth最小值可能低至1.5V,最大值可达4.5V)。这是一个必要条件,但非充分条件——仅表示沟道开始形成,而非完全导通。

二、阈值电压Vth的完整特性

2.1 Vth的温度依赖性

Vth具有负温度系数,约-4mV/℃。这意味着:

在低温环境(-40℃)下,Vth可能升高0.3V,需要更高的VGS才能导通

在高温环境(150℃)下,Vth降低0.6V,导通更容易,但关断可靠性下降

工程要点:设计时必须按Vth_max(考虑低温最坏情况)确保驱动电压足够,同时按Vth_min(考虑高温最坏情况)防止误导通。

2.2 Vth的批次离散性

同一型号器件的Vth存在离散性,规格书给出范围如Vth = 2.0V to 4.0V。批量应用时,驱动设计必须覆盖此全范围,不能按典型值3V设计。车规级器件通过严格筛选,可将Vth范围压缩至2.5-3.5V(σ<0.15V),显著降低设计难度。

2.3 体效应(衬偏效应)

当源极与衬底间存在电压差VSB时,Vth会随之变化:Vth = Vth0 + γ(√(2φf + VSB) - √(2φf))其中γ为体效应系数。在功率NMOS中,衬底通常与源极短接,VSB=0,可忽略此效应。但在某些模拟电路中,需考虑Vth偏移。

三、完全导通的深层条件

当VGS > Vth后,NMOS进入线性区(欧姆区),但要实现完全导通(即导通电阻R_DS(on)达到最小值),还需满足:

3.1 足够的栅极驱动电压

规格书通常标注 R_DS(on) @ VGS = 10V ,这意味着在VGS=10V时,沟道完全开启,R_DS(on)达到标称值。若驱动电压不足:

VGS = 4.5V(逻辑电平驱动):R_DS(on)可能比10V时增加50-100%

VGS = 3.3V:器件仅微弱导通,R_DS(on)极大,功耗剧增,极易烧毁

工程铁律:驱动电压必须≥规格书测试电压(通常10V),并留2V裕量。对于逻辑电平MOS管(Logic Level FET),虽标称VGS=4.5V,但仍建议驱动至8-10V以获得最佳性能。

3.2 漏源电压VDS的限制

完全导通要求VDS足够小,满足VDS << VGS - Vth。此时沟道未在漏极端夹断,器件工作于线性区。若VDS过高(如VDS > VGS - Vth),沟道在漏极端夹断,器件进入饱和区(恒流区),此时虽导通但呈现恒流特性,R_DS(on)失去意义。

判断公式:线性区(完全导通):VGS > Vth 且 VDS < VGS - Vth饱和区(不完全导通):VGS > Vth 且 VDS ≥ VGS - Vth

在开关应用中,导通态VDS = ID × R_DS(on)通常<0.5V,满足线性区条件;在放大应用中,VDS较高,工作于饱和区。

3.3 足够的驱动电流(动态导通)

对于开通瞬态,驱动电路必须提供足够的栅极充电电流Ig,使VGS在目标时间内上升到驱动电压。若Ig不足:

开通时间tr延长,开关损耗剧增

器件在R_DS(on)较大状态下停留时间过长,瞬时功耗可能超标

驱动电流需求:Ig = Qg / t_target,其中Qg为总栅极电荷(如60nC),t_target为期望开通时间(如50ns),则Ig需达1.2A。驱动芯片峰值电流应≥1.5Ig。

3.4 栅极电荷完全充满

完全导通要求栅极电荷达到Q_g_total,包括:

Qgs:栅源电荷,建立沟道

Qgd:米勒电荷,克服米勒平台

Qod:过驱动电荷,使VGS达到最终值

若驱动在米勒平台前停止,VGS仅达Vth + ID/g_m(约5-6V),此时沟道虽形成但R_DS(on)未达最优,处于半导通状态,极其危险。

四、实际应用中的导通条件设计

4.1 驱动电压设计

标准NMOS:驱动电压12-15V,确保所有器件完全导通

逻辑电平NMOS:驱动电压8-10V(尽管4.5V可导通)

特殊应用:高压侧NMOS需自举驱动,自举电压需> Vth + 5V

4.2 驱动电路要求

驱动电阻Rg:取值10-50Ω,平衡开关速度与EMI。Rg过大导致tr延长,Rg过小引起振荡

驱动芯片:峰值电流需>1.5A,确保快速充电

负压关断:在车规或高温应用中,关断时施加-3V至-5V负压,确保VGS < Vth_min(高温下可能降至1.5V)

4.3 温度与散热考量

导通后损耗P_cond = ID² × R_DS(on)。若ID=50A,R_DS(on)=10mΩ,则P_cond=25W。温升ΔTj = P_cond × θ_jc(θ_jc≈0.5℃/W),ΔTj=12.5℃。若环境温度85℃,则Tj=97.5℃,远低于150℃,导通可持续。

反之,若ID=80A,R_DS(on)=20mΩ(因VGS不足或温度高),P_cond=128W,ΔTj=64℃,Tj将达149℃,接近极限,长期运行不可靠。

五、常见误区与失效模式

5.1 误区:VGS > Vth即可导通

错误:仅施加3V(Vth典型值)驱动,认为已导通后果:器件处于临界导通,R_DS(on)可能是标称值的5-10倍,功耗数十倍增加,瞬间烧毁

5.2 误区:忽略温度对Vth影响

错误:室温下调试正常,高温环境下关断时未加负压后果:高温下Vth降至1.5V,若关断时VGS=0V,可能因噪声耦合(>1.5V)导致误导通,桥臂直通,系统崩溃

5.3 误区:驱动电流不足

错误:使用弱驱动(Ig=0.5A)驱动大Qg(100nC)器件后果:开通时间tr=200ns,开关损耗剧增,效率低下,器件过热

5.4 误区:静态导通时VGS回退

错误:用MCU GPIO(3.3V)直接驱动MOS管栅极后果:VGS=3.3V仅略高于Vth,无法完全导通,看似工作实则处于危险放大区

六、总结:导通条件的完整表述

NMOS的可靠导通必须同时满足以下条件:

电压条件:VGS ≥ Vth_max + 5V(通常10-15V),且VDS < VGS - Vth

电荷条件:栅极电荷完全充满至Q_g_total,通过米勒平台

电流条件:驱动电路提供足够Ig = Qg / t_target

温度条件:结温低于150℃,确保参数不漂移

时间条件:在目标时间内完成导通,避免长时间高R_DS(on)状态

记忆口诀: "电压要够高,电流要管饱,电荷得充满,温度别超标"

在工程实践中,默认驱动12V可覆盖绝大多数NMOS,Rg取值10-20Ω可平衡速度与EMI,栅极对源极并10kΩ电阻可确保关断可靠,这些经验法则简化了导通条件的设计验证。