在高速串行数据传输、AI 运算、电信基站、PCIe 接口等对时钟稳定性与抗干扰能力要求严苛的场景中,差分晶振早已成为核心时钟器件,其性能直接决定了整套系统的信号传输质量与运行可靠性。

差分晶振是一种输出两路极性相反时钟信号(P 端与 N 端)的有源振荡器,这是它与普通单端输出晶振(XO,如 CMOS 输出型)最核心的区别。正是这种差分输出结构,赋予了它远超单端晶振的两大核心性能优势:极强的共模干扰抑制能力与超低的相位抖动。

所谓共模抑制比(CMRR),是衡量差分信号对抵消外界电磁干扰、电源噪声等共模噪声的能力指标,这也是差分晶振能在复杂电磁环境的工业、通信、车载电路中保持稳定输出的核心原因。

而另一项决定高速传输性能的核心指标相位抖动,指的是时钟信号在时间轴上的微小偏移,该参数直接决定了高速数据传输的误码率。普通单端晶振的抖动性能无法满足千兆级以上高速传输的要求,而高性能差分晶振在 12kHz-20MHz 频段的相位抖动通常可控制在 50fs 到 200fs 之间,完全适配高可靠性的高速场景需求。也正是因此,在需要极高串行数据速率(SerDes)的 AI 运算场景中,差分晶振是必选的时钟方案,单端晶振因抖动过大,无法满足 AI 算力平台对超低误码率的传输要求。

目前行业内差分晶振的主流输出逻辑主要分为 LVPECL、LVDS、HCSL 三大类,三类产品各有特性,适配不同的应用场景。

其中 LVPECL 输出的核心特点是输出幅度大(约 800mV),信号质量优异,缺点是功耗相对较高,是电信基站等通信设备中最常用的差分时钟输出类型;

LVDS 输出凭借低电压摆幅(约 350mV)的特性,实现了极低的功耗与极小的电磁干扰(EMI),是通用高速数据传输场景的首选方案,广泛应用于各类对功耗与 EMI 控制有严格要求的工业与消费电子设备中;HCSL 输出则是 PCI-Express (PCIe) 接口的标准时钟逻辑,拥有极快的上升沿速度,专为高速串行总线设计,是计算机、服务器、存储设备中 PCIe 接口的标配时钟方案。

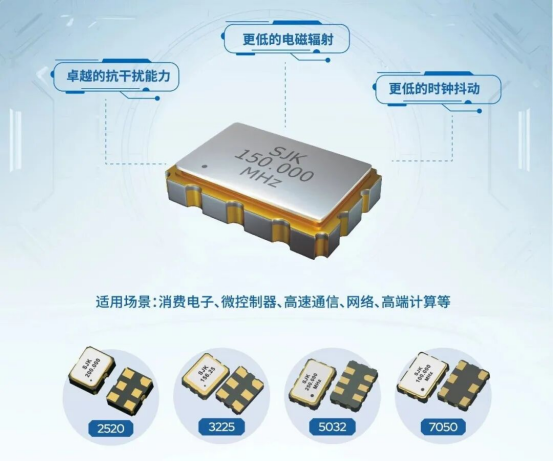

在明确了输出类型之后,硬件设计与采购环节需要重点关注差分晶振的核心规格参数,这是选型匹配的核心依据。目前行业内差分晶振的常规频率范围在 10MHz 到 700MHz 之间,高端定制化产品的频率可达到 2GHz 以上,可覆盖绝大多数高速场景的时钟需求。

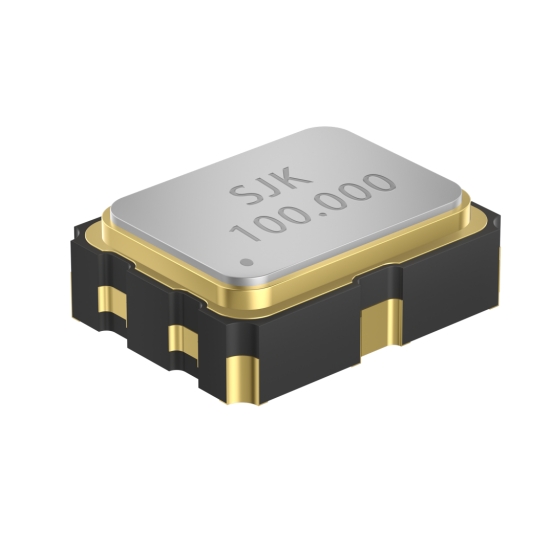

引脚定义与供电特性同样是选型的核心要点,目前行业通用的 6 脚封装差分晶振,标准引脚定义为:1 脚 OE(使能)、2 脚 NC(空脚)、3 脚 GND(地)、4 脚正向输出端、5 脚互补输出端、6 脚 Vcc(供电)。其中 OE 引脚为输出使能控制端,高电平时晶振正常输出时钟信号,低电平时关闭输出,进入省电模式,可适配低功耗场景的电源管理需求。

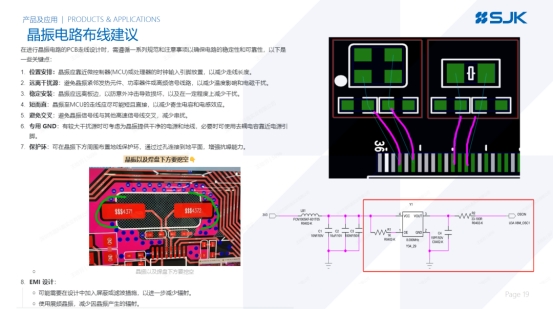

差分晶振的性能发挥,高度依赖匹配的电路设计与 PCB 走线规范,核心设计要点主要分为阻抗匹配与差分走线控制两部分。不同输出类型的差分晶振,有对应的标准匹配要求,错误的匹配会直接导致信号质量劣化、EMI 超标:LVPECL 输出通常需要配置到 Vcc-2V 的偏置电阻;LVDS 输出需在接收端跨接 100Ω 的终端匹配电阻;HCSL 输出则需要在源端串联 33Ω 的匹配电阻。

(相关详细资料可私SJK晶科鑫了解)

差分走线方面,差分信号的传输对 PCB 走线有严格要求,核心原则是保证差分对的阻抗一致性与信号同步性。差分走线必须保持等长、等宽、紧耦合,同时尽量减少过孔的使用,避免出现阻抗不连续的问题。

差分晶振作为高速电路的时钟核心,其选型、设计、测试的每一个环节,都直接影响系统的最终运行效果,只有充分理解其核心原理与应用规范,才能最大化发挥其性能优势,保障高速系统的稳定可靠运行。