近日,关于CMOS电路中背面电源连接的技术探索备受关注,首个集成背面电源连接的CMOS电路可能采用基于堆叠的纳米片晶体管。然而,未来的发展路径引人关注,规划者构想了一种新型的互补晶体管(CFET),它将垂直集成堆叠的NFET和PFET器件,为电路设计带来全新的可能性。

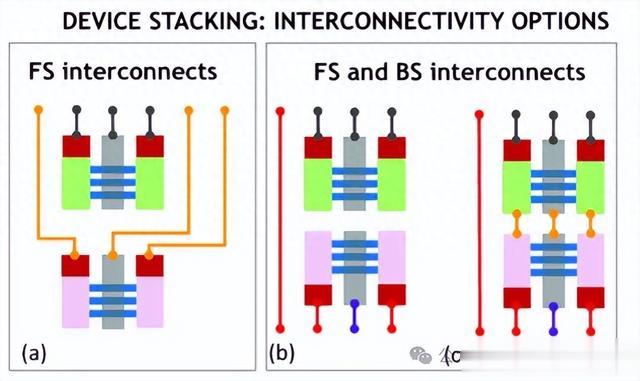

CFET的厚度至少是纳米片晶体管的两倍,这意味着将CFET彼此连接以及与电路其余部分连接将面临任何互连方案的挑战,无论是使用背面、正面还是两者兼用的方案。

在管理中间电介质方面,从CFET的顶部器件到底部电网的接触需要高宽高比的蚀刻。英特尔将这一过程视为其PowerVia方案的扩展,而不是彻底的改变。然而,与纳米片晶体管相比,CFET需要一个中间介电层来隔离NFET和PFET。

根据集成方案的不同,这一层可以在开始时作为Si/SiGe异质结构中的介电层创建,最终形成纳米片结构。另外,产生和隔离通道纳米片的选择性蚀刻和氧化步骤也可以为中间介电层产生更厚的氧化物。管理CFET的散热仍然是一项正在进行的工作。一旦构建了CFET,无论是单片还是顺序,下一个大问题是散热。在芯片层面,背面电源有助于散热。更粗的电源线电阻更小,并提供一个热路径到设备的背面。然而,在任何特定地点,采暖量仍然取决于工作量和当地环境。将器件与背面分开的介电层是热传递的屏障。

即使整体的热提取是充分的,也可能出现热点,而没有大块硅衬底的热扩散作用。在12月的IEEE电子器件会议上,Imec的Anabela Veloso及其同事指出,用SiN取代SiO2屏障氧化物可能会改善热量传播并降低热点的风险。

根据英特尔的PowerVia架构,CFET将带来新的散热挑战。添加更多的纳米片会降低每一层的电流密度,从而减少加热,但也会增加电容。通道分裂成平行的纳米片降低了散热,因为中间的介电层是热传输的屏障。尽管增加片数会降低电流密度,但研究表明,积极的缩放会带来巨大的热成本。

在电路噪声管理方面,英特尔的PowerVia架构在前端集成了噪声屏蔽,以取代信号线之间的隔离效果。

总的来说,背面电源技术和CFET的出现为CMOS电路的发展提供了新的动力和挑战。未来,随着技术的进一步发展,背面电源和三维堆叠结构有望成为行业追求更紧凑、更强大系统的关键技术。

欢迎关注芯片行业动态!