1,背照式技术

在背照式技术出现之前,CMOS图像传感器都是前照式的结构,当光经过微透镜和颜色滤镜后还要经过金属布线层——可将电压信号转换为数字信号,才能到达光电二极管处并因此开始累积光生电子。

然后复位晶体管 RX 打开将浮置扩散区电容复位,同时选择晶体管 SX 导通,将经过放大晶体管 DX 增强的电压值传输到金属布线层处,此即为复位读出。

然后传输晶体管 TX 导通,将光电二极管积累的信号电荷转移至浮置扩散区电容,再继续重复上面的过程以完成信号读出。最后信号读出与复位读出的差值,便是能够消除复位热噪声的有效信号值。

在这个过程中,金属布线层受到光照时会发生反射和衍射现象,假如像素够大的话这并非大问题。

但是随着手机端传感器像素尺寸的缩小,这两种现象所导致的问题就会变得非常严重。

首先反射的影响很简单,毕竟像素尺寸越小进光量就越小,这反射所造成的损失就很明显了。

至于衍射问题,则是因为金属布线层的间隙,随像素缩小变密后使得光通过时的衍射现象增强了,最终导致图像中的颜色混合在一起。

而根据衍射计算公式可以知道,若要改善单个区域的衍射问题,就必须缩短微透镜到光电二极管的距离。

为了一次性全部解决反射和衍射问题,豪威首创的背照式技术就此应运而生,并由2010年发布的iPhone4在手机端首发了这个先进技术。

这个技术具体来说就是先在晶圆的一侧制作所有的电路部分,然后将晶圆翻转倒置在处理基板上,接着将上面硅层打薄以便创建可以在背面收集光线的光学结构。

这样既可以消除前照式结构中金属布线层造成的衍射干扰,又能解决之前金属布线层阻碍光线通过所造成的反射问题,从而得以在同一大小像素条件下提高光电量子效率。

此外,由于金属布线层被转移到了背面,这样就可以“肆无忌惮”地拓展电路规模,以提升传感器的读取速度!从而实现更高速的连拍和更高清的视频录制。

2,堆栈式技术

随着智能手机的不断发展,对图像传感器性能之需求开始日益增长,同时传感器的小型化趋势也日益明显。

而要提高传感器的处理性能,就得增加处理回路的晶体管数量,简而言之就是得提高制程,从而在同等面积内容纳更多的晶体管。

但尴尬的是,与处理回路处于同一层的像素区域,对制程工艺却并不“感冒”(与像素尺寸有关)。

例如,像素区域用65nm的制程就非常足够了,但对于处理回路来说若能将制程提升至45nm则可将晶体管数量提高一倍!

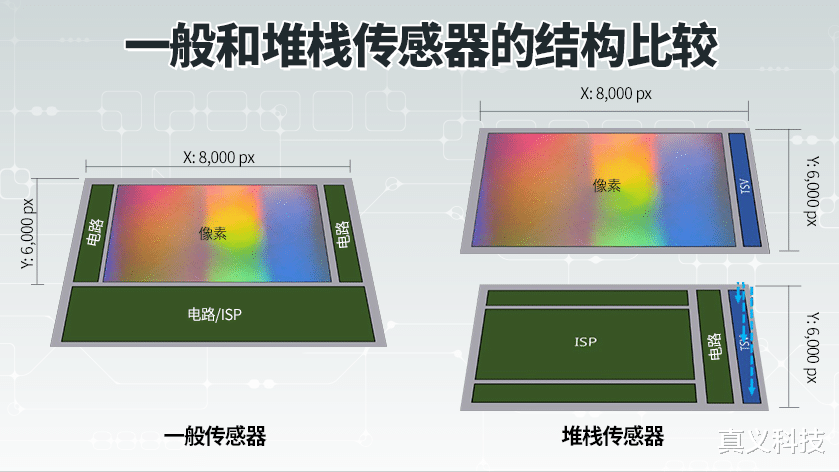

于是索尼便想到了,将像素区和电路区分离并堆叠在一起的解决方案,这样两者就可以在不同的制程条件下单独制造了。

此外,该方案因为首层没了电路区所以就没那么“拥挤”了,又由于电路区有了自身的单层“独栋别墅”故规模得以大幅扩张!

此番操作过后,由于像素层依然可以采用背照式技术,所以之前背照式的优点得以全部继承。

此外,若像素层的面积不缩小,则可在之前处理回路所占的区域种植更多的像素,这又为小型高像素路线奠定了基础。

另外处理回路在单独分层后,在更先进的制程工艺和更大的堆料面积之双重加成下,还有其它惊喜!

例如,分层后电路区可以配置性能更强功耗更低的图像信号处理器以及配套电路,从而实现硬件级HDR以及慢动作拍摄等功能。

像素层与电路层分离后,最初的方案是采用硅通孔技术 TSV 将两层连接在一起。

后来工艺进步了又引入基于Cu-Cu互连的混合键合技术,该技术不仅提高了读出速度,还进一步实现了传感器的小型化并促进了生产效率!

3,双层晶体管技术

在堆栈式技术之后,索尼还首创了“三层堆栈式”结构——在90nm的感光层和40nm的电路层之间额外加入了30nm的DRAM层,从而得以支持最高1000fps的超慢速视频拍摄,并大幅改善了“果冻效应”。

但由于这个技术成本高,且在手机上应用问题还不少,所以更多还是应用在相机端,移动端主要是索尼和三星以前的旗舰手机在用。

此后索尼并没有停下脚步而是又开始在像素层折腾了,并首发了光电二极管与像素晶体管分离的双层晶体管技术,以期用同样大小之底实现更佳的光电性能——即更大的动态范围和更少的暗光噪点。

在传统工艺的像素结构中,光电二极管和四类像素晶体管虽然聚集在一起,但像素晶体管却并不参与感光。于是索尼便将,除了 TX 晶体管之外的其它三类像素晶体管,单独分离聚于一层。

最终的“疗效”极为显著,因为满阱容量得益于此直接翻倍式增长!这就代表着传感器的动态范围也获得了巨幅提升。

此外由于 SX、RX、DX 三类像素晶体管单独处于一层,少了光电二极管的空间挤占,便能将 DX 晶体管的尺寸做大,从而让暗光场景的弱电压信号得到更大的增益,使得最终图像噪点明显减少。