二.跨模块ESD设计

现阶段芯片的集成程度越来越高,同一个芯片内可能集成数字电路,模拟电路,射频电路模块。不同模块的Power/GND与通信线具有ESD高失效风险,所以需要重点关注。

2.1 跨模块VDD/GND防护策略。

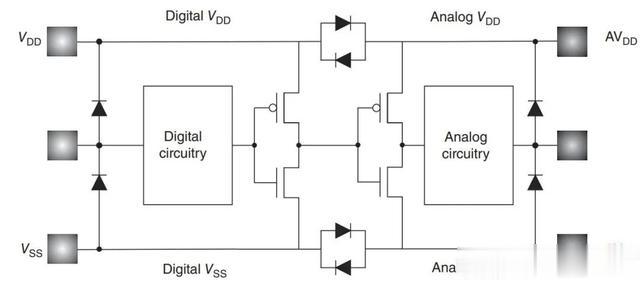

因为不同模块被集成到一个芯片内,所以除了模块内部的ESD器件外,还需要设计针对全片的ESD防护网络。但又要最大程度的隔离模块间的干扰,尤其是降低数字模块对模拟和射频模块的影响。(数字电路以逻辑门为主,会对VDD/GND频繁抽放,造成VDD和GND不稳定)模块内部的ESD设计暂且不表。如图一所示,模块间VDD/GND的ESD防护策略主要有三种:DVDD-AVDD,DVDD-AVSS、AVDD-DVSS,DVSS-AVSS。

图一A.AVDD-DVDD,B.DVDD-AVSS,C.DVSS-AVSS。

第一种是在DVDD与AVDD之间建立ESD网络,第二种是在VDD与VSS建立交叉ESD网络,第三种是DVSS-AVSS间建立ESD网络。采用何种方案需要根据电路实际情况与设计需求进行选择,这三种设计都各有千秋。第三种设计是最为常见的跨模块ESD设计,只需要少量器件就能实现GND之间的解耦和ESD泄放,且不需要计算Design Window。不过这种设计的也有其弊端,DVDD—AVDD的ESD泄放需要先利用Power Clamp到达DVSS,然后通过跨模块ESD网络到达AVSS,最后到达AVDD。这期间不仅要流经众多ESD器件,而且路径较长,会有一定的回路电阻,导致ESD压降较大,容易造成TX端PMOS失效,降低ESD鲁棒性。而第一种不是很常见,如果DVDD与AVDD电压不一致的话,还需要设置Design Window,同时ESD器件直接跨接在DVDD与AVDD之间,还会面临着很高的Latch up风险。第二种更为罕见,不过能有效降低ESD压降,对电路内部TX端和RX端的PMOS,NMOS保护也最为到位,能大幅提高ESD鲁棒性,不过所需要的面积也是三种中最大的。

2.2 跨模块ESD防护器件。

如图二所示,早期设计中会使用电阻作为跨模块ESD器件,虽然电阻对面积要求较低,但是电阻对于噪音的隔离效果不理想,总会存在漏电流,且会提高回路电阻,造成意想不到的风险。

图二.Power/GND 电阻隔离。

如图三所示,现阶段主要使用双向二极管串作为跨模块ESD器件,二极管的开关特性能有效泄放ESD电流和隔离噪音。而二极管的数目是由正常工作下两边的压差和噪声隔离电压/电容所决定(GND上的双向二极管串不需要考虑GND间的压差,只需隔离数字GND上发生的地弹)。在VDD间采用双向二极管串时,需要预防VDD浪涌造成双向二极管串发生误开启。

图三.Power/GND 双向二极管串隔离。

如图四所示,有些设计会在DVDD与AVDD间放置NMOS作为跨模块ESD器件。这种设计能一定程度提高DVDD-AVDD间的ESD泄放效率,但是该NMOS的Design Window很难定夺。如果Design Window 过低,虽然能提高ESD效率,但是Latch up风险也同时会增大。如果Design Window 过高,该元器件的泄放效率可能会打折扣,且ESD电流会从Power Clamp→双向二极管串→Power Clamp实现泄放。除此之外,若Power Clamp采用RC-detector频率触发模式,该电压触发的NMOS便是画蛇添足。(这里提出一个概念:ESD防护器件一致性,如果全片采用了RC-detector频率触发单元作为Power Clamp,就尽量不再采用GGNMOS,SCR等电压触发ESD器件。)

图四.Power NMOS 隔离。

2.3 模块间通信线ESD防护。

图五.模块通信线示意图。

如图五所示,跨模块ESD防护的重点除了Power Rail外,还需要关注模块间的通信线,其具有较高的CDM失效风险。TX端在外界因素下会在衬底内积累电荷,不仅会带来自身栅极的失效风险,还会对RX端栅极造成风险。

图六.模块间通信线CDM失效示意图。

如图六所示,正向CDM下,MpT的栅极会有失效风险。同时MnT衬底中的大注入载流子需要从回路:VSS1→Bidirectional Diode→VSS2→Power Clamp→VDD2流出体系,一旦该回路ESD压降过高,MpR栅极就会面临失效风险。同理,负向CDM下,MnT的栅极将会面临CDM冲击,同时MpT中的CDM电流需要从回路:VDD1→Power Clamp→VSS1→Bidirectional Diode→VSS2流出体系,如果该回路压降过高,CDM电流就会有击穿MnR栅极的风险。

图七.模块间通信线CDM防护示意图。

为了降低CDM失效风险,需要对模块间通信线进行CDM防护。如图七所示,常规方案是在RX端添加二极管或者二级Power Clamp,给予RX端栅极额外的防护,提高ESD鲁棒性。但是这会在通信线上增加寄生电容,在某些情况下,电路设计人员并不能容忍通信线上增加寄生电容。如图八所示,可以采用Soft Tie ESD电路对RX端进行保护,从而避免在通信线上引入器件。

图八.Soft Tie ESD保护电路。

图九中,利用VF-TLP对Soft Tie ESD电路的性能进行表征,Soft Tie ESD电路能有效提高VDD1—VSS2和VDD2—VSS1路径的CDM鲁棒性。

图九.Soft Tie ESD电路的VF-TLP性能。

如图十所示,除了Soft Tie ESD外还可以采用Stack 结构对通信线施加CDM防护。

图十.Stacking MOS ESD防护电路示意图。

2.4 多功能域布局。

IC内一旦集成数字,模拟,射频等多模块后,就需要利用布局布线对不同模块进行隔离,从而最大限度减少干扰,并提高ESD鲁棒性。

图十一.数字、模拟、射频多模块布局。

在布局时,避免数字模块与模拟模块相邻,减少干扰。芯片的角落不能放置核心电路,可以把Power Clamp放置到角落。而无论是模拟模块还是数字模块,都需要ESD Rail 形成环路,构成完整的ESD回路。而实际设计中全局布局布线是一项很复杂的设计,需要综合各方面因素,草草几句很难说清楚。