文:王世权 编辑:练怡萍

2024年5月22-23日,由雅时国际(ACT International)主办,国家第三代半导体技术创新中心(苏州)、宽禁带半导体国家工程研究中心、宽禁带半导体器件与集成技术全国重点实验室、国家集成电路特色工艺及封装测试创新中心承办2024-半导体先进技术创新发展和机遇大会苏州狮山国际会议中心成功举办,冯明宪博士受邀参加“CHIP China晶芯研讨会”分论坛,并作主题报告:CoWoS:技术、生态与投资。

CoWoS技术作为目前先进AI算力芯片一致采用的封装技术,是提升AI算力芯片性能提升、产能释放、市场竞争力的最重要因素之一,因此冯明宪博士依据亚太芯谷科技研究院提出的CoWoS分析架构,从哲学、技术、产业/生态、资本、国家/地区五个维度对CoWoS技术进行系统解析,下面与大家分享报告的主要内容:

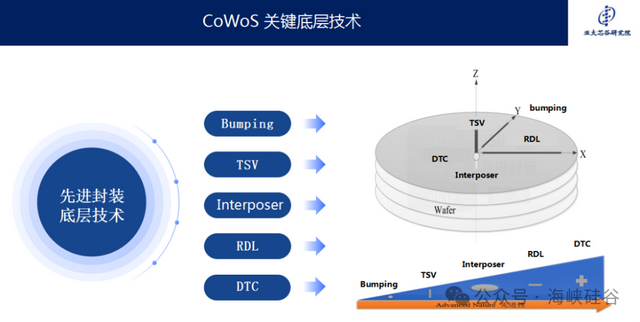

CoWoS封装技术是由一系列的底层技术组成,其中最关键的几种底层技术分别是:

Bumping、TSV (Through-Silicon Via)、Interposer、RDL (Redistribution Layer)、DTC (Direct Through Chip)。

凸块制造技术(Bumping)是一项关键的先进封装技术,它通过在芯片表面制造金属凸块来提供电气互连的“点”接口。这一技术在多个先进封装应用领域广泛应用,包括FC、WLP、CSP、以及3D封装等。

凸块指的是定向生长在芯片表面的金属凸起结构,它们与芯片焊盘直接或间接相连,具备金属导电特性。凸块工艺位于整个产业链的关键位置,处于集成电路制造和封装测试之间,因此被视为先进封装领域的核心技术之一。

其技术的基本原理如下:

晶圆制程后的加工: Bumping技术通常在晶圆制程的后阶段进行。晶圆制程包括完成IC电路部分的加工,而Bumping则在此之后进行,用以在晶圆的I/O端口的Pad上形成焊料凸点。

凸点形成过程: 在Bumping过程中,通常会将焊料材料(通常是锡合金)涂覆或以其他方式添加到晶圆的特定区域,这些区域通常是I/O端口的Pad。随后,焊料会被加热,以形成小型的凸点,这些凸点用于连接晶片和其他封装组件,如基板(substrate)。

用途: Bumping技术的主要目标是确保晶片与其他封装组件之间的可靠连接。这种连接可以通过焊接等方法来实现,以便有效传输信号和能量。

随着封装技术的演进,凸块技术也向着更高密度、更小微间距方向发展。因此,在2.5D与3D先进封装中,凸块的尺寸至关重要,一般铜微凸块比焊球/凸块更小,可在封装中实现更多 I/O。当前,先进封装技术的微凸块间距最小达40μm,这相当于20μm至25μm的凸块尺寸,裸晶上相邻凸块之间的间距为15μm。

对于小于400μm的间距,在封装上有另外一些选择,即首先可以使用现有的凸块技术研发新的封装技术,以突破技术瓶颈,将当前400μm间距向下微缩至100μm。或者,另一种选择是被称为铜混合键合的新技术。在混合键合技术中,裸晶的连接并非通过封装中的凸块。相反,该技术利用微小的铜对铜互连,实现比传统封装具有更多I/O的更窄间距封装。对于封装技术来说,混合键合的间距至少在10μm及以下。

在第一种方案中,随着焊料/铜凸点技术逐渐向更窄间距微缩,对于新材料、新工艺和新工具的需求越来越多,随之挑战也大幅增加。而第二种方案,则面临着成本高昂技术苦难的局面,仅能应用在高端产品上,有较大的技术研发与应用局限。

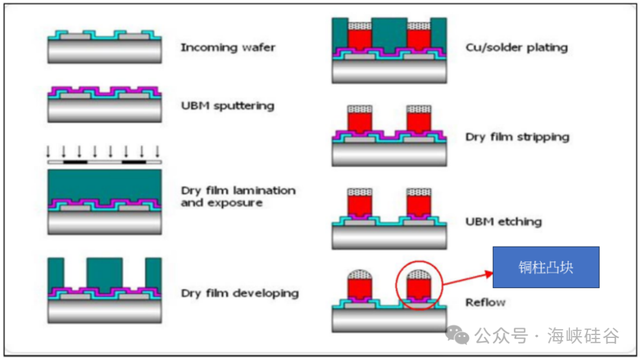

铜柱凸块制程示意图

TSV硅通孔是实现容量和带宽扩展的核心,根据国际半导体技术发展路线图(ITRS),TSV定义为:连接硅圆片两面并与硅衬底和其他通孔绝缘的电互连结构。由此可见,TSV是一种垂直互连结构,特点是穿透硅衬底,并实现从对应电路层一面到另一面的电气连接。根据硅通孔的定义,可以知道,TSV的基本结构包括穿透硅衬底的导电通道,以及与衬底之间的绝缘隔离层。并且,为了实现衬底上下面的电气连接,还需要正面和背面的互连层,以实现信号的互连和再分布。

TSV概念最早可以追溯到1958年,威廉·肖克利(William Shockley)提出了一份专利申请“Semiconductive wafer and method of making the same”首次提出了硅通孔(TSV)结构,并获得专利批准。肖克利提出的TSV主要作用有两个,其一,实现芯片正反之间的电导通,其二,是有利于热管理,即更好的释放热量并提高热管理性能。经过几十年的发展,目前应用最广泛的是Cu-TSV,即硅通孔(TSV)中填充铜,而使用铜作为TSV填充材料的3D集成封装,主要是日本超级先锋协会首创电子技术联盟(1999-2003年)率先实现的。

2006年,三星电子发布了较为简单的存储芯片堆叠示意图,这些芯片大部分属于DRAM(动态随机存取存储器)或者I/O数量少于100的NAND闪存(I/O数量比较确切的是78个)。这种存储芯片附在有机基板上,即使采用8个芯片堆叠,它们总体的厚度(560μm)仍然小于普通芯片的厚度,但是考虑到综合生产成本与引线键合技术的成熟封装量产的竞争,使用硅通孔(TSV)技术的存储器芯片堆叠并未进行大规模量产。

在HBM设计制造中,通过在整个硅晶圆厚度上打孔,在芯片正面和背面之间形成数千个垂直互连。在HBM中多层DRAMdie堆叠,通过硅通孔和焊接凸点连接,且只有最底部的die能向外连接到存储控制器,其余管芯则通过内部TSV实现互连。

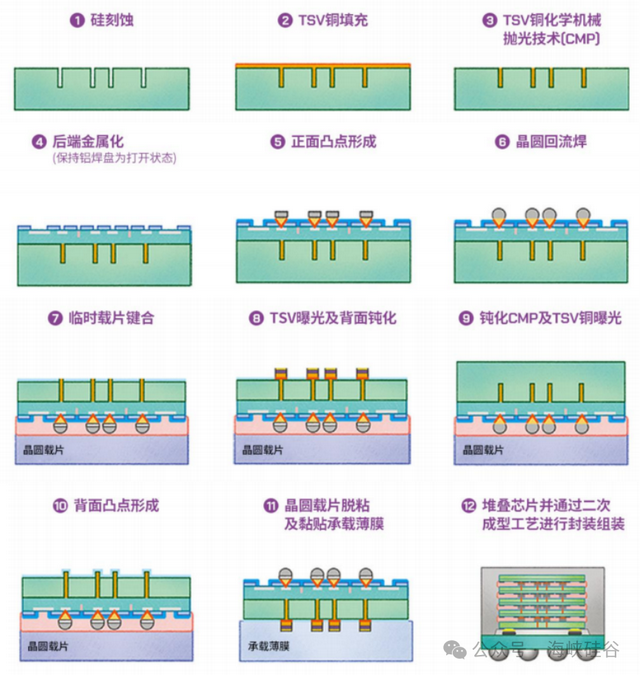

TSV工艺包含晶圆的表面清洗、光刻胶图案化、干法/湿法蚀刻沟槽、气相沉积、通孔填充、化学机械抛光等几种关键工艺,运用到晶圆减薄机、掩膜设备、涂胶机、激光打孔机、电镀设备、溅射台、光刻机、刻蚀机,同时配套的电镀液、靶材、特种气体、塑封料等。

TSV工艺流程

中介层Interposer在CoWoS技术中扮演着重要的角色,它帮助上层或下层的节点之间进行信息交换,特别是连接两个芯片。Interposer通常使用微凸点(ubump)和C4凸点(C4 bump)与芯片、封装基板进行电性能互连,实现芯片与封装基板之间的信息交换。其一般可以由硅和有机材料构成。

与倒装芯片封装相比,中间层是一种附加组件,位于层压基板和顶部芯片之间,是有基硅和有机(RDL,再分布层)的中间层工艺。中间层提供了异质集成的互连和细密间距微凸点。基于焊料的微凸点不仅提供了自对准的连接,还最小化了对器件的热预算的影响。中间层使用晶圆工厂的光刻工艺制造线路和通孔。它在创造高通孔数时比激光钻更具成本效益和精度。中间层还作为应力缓冲器,减小了顶部芯片和基板之间的热膨胀系数(CTE)不匹配应力,增强了封装的可靠性。

中介层是顶部芯片和层压基板之间的附加组件。

中介层上的各种互连

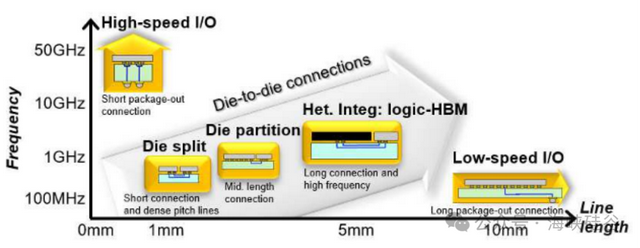

下图图显示了中间层上各种信号互连与线长和工作频率的关系。高速I/O使用短的垂直路由路径,具有低插入损耗和耦合,而低速I/O则使用长路由线,用于从硅芯片到中间层边缘的信号扩展。中间层上有三种芯片对芯片(D2D)连接方式。第一种是用于具有相同功能的硅芯片的芯片分裂互连,它们通过短而高密度的细密间距线路相互连接。第二种是用于不同功能的逻辑芯片的芯片分区互连,它们通过中等长度的线路相互连接。第三种是用于不同功能组件的异质集成互连,如HBM和光学器件,它们通过长线路相互连接。随着数据速率越来越高和互连长度越来越长,例如HBM-SOC连接,情况变得更加具有挑战性。

中介层上的各种信号互连与线路长度和工作频率的函数关系。

(4)RDLRedistribution layer (再分布层,RDL),是添加到集成电路或微芯片中以重新分配电气连接的金属层。这种RDL技术是一种用于集成电路(IC)的先进封装解决方案,允许将多个芯片集成到单个封装中。它是在介电层顶部创建图案化金属层的过程,该金属层将 IC 的输入/输出 (I/O) 重新分配到新位置。新位置通常位于芯片的边缘,这允许使用标准表面贴装技术 (SMT) 将 IC 连接到印刷电路板 (PCB)。RDL 技术使设计人员能够以紧凑、高效的方式放置芯片,从而减少器件的整体尺寸。

RDL的主要功能包括:

1)提供水平接口连接:RDL包含主要的水平接口连接,提供晶片之间的连接。这些连接可以在晶片的顶部进行,并且RDL的结构类似于HDI PCB中的盲/埋微孔。

2)提供高密度互连:在先进封装技术中,例如超高密度InFO(InFO_UHD)技术,RDL被开发为提供逻辑-逻辑系统的高互连密度和带宽。例如,该技术的带宽密度可以达到线宽和间距(L/S)为0.8/0.8 μm,长度为500 μm的逻辑-逻辑系统的记录高度10 Tbps/mm。

3)实现异质集成:RDL在实现异质集成方面也起着重要作用。异质集成是一种将独立设计和优化的元件集成到一个共同的interposer上的过程,这对于制造更高速度和性能的元件至关重要。RDL技术使得元件可以更接近地放置,从而最小化了用于补偿互连线中的频率依赖性损耗的寄生功耗。

Interposer中的RDL层包含主要的水平接口连接,用于在interposer顶部的元件晶片之间建立连接。RDL的结构类似于HDI PCB中的盲孔/埋孔技术。Interposer中的RDL层包含主要的水平接口连接,用于在interposer顶部的元件晶片之间建立连接。RDL的结构类似于HDI PCB中的盲孔/埋孔技术。

在台积电的RDL技术中,提供不同芯片之间的亚微米间距RDL的能力是硅中间层的一个关键优势,可以直接利用晶圆厂工艺。通过高频结构模拟器(HFSS)评估了三种金属方案(表一)的性能比较。每种金属方案的信号回波损耗和插入损耗如图 4-4所示,表明较厚的金属可提供更好的信号完整性。然而,较厚的金属意味着较差的宽度/空间,并导致较低的布线密度。对于具有大量芯片间布线要求的产品,这不是首选。因此,考虑不同产品的工作条件和带宽,选择合适的RDL方案是电路设计人员的一项重要任务。一般来说,带有硅中介层的 CoWoS 与硅晶圆厂中可用的任何类型的金属方案兼容,以满足芯片间互连的整体性能和布线需求。

TSMC 提供的 Si Interposer RDL 金属方案

不同 RDL 方案上 (a) 回波损耗和 (b) 插入损耗的 HFSS 仿真结果

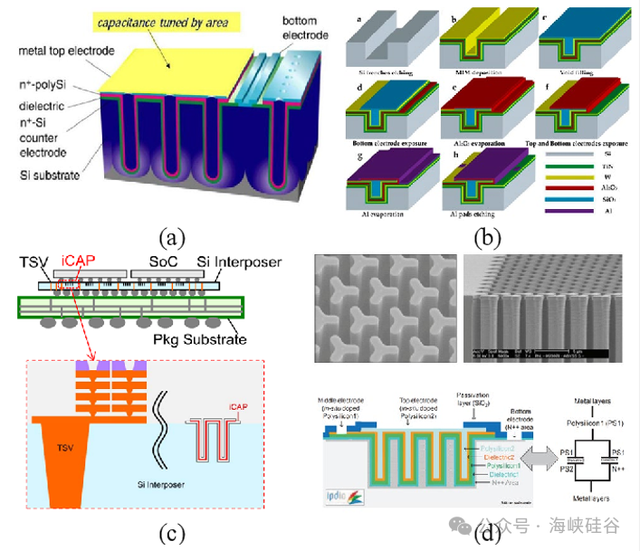

(5)DTC在异构集成中,通常使用基板(一般为硅中介层)来实现电源和组件之间的互连。随着对性能和互连密度的要求不断提高,必须在转接板上使用去耦电容器,以解决日益严重的 EMI 问题。硅电容器技术,特别是深沟槽电容器(DTC)技术,由于具有小尺寸和CMOS工艺兼容性等优点,非常适合基于硅中介层的集成。

也因此,台积电在CoWoS中采用了DTC技术。

CoWoS平台引入的第一代深沟电容器(eDTC)技术可以将系统的电源分配网络(PDN)阻抗降低93%,第一电压下降比没有eDTC低72%。此外,在3.2 GHz时,HBM中VDDQ的同步切换噪声(SSN)相对于没有eDTC的情况下可以减少38%。信号完整性也可以得到改善,因为SSN减少了。具有eDTC的CoWoS平台有助于提高电源完整性和信号完整性。新一代的eDTC可以提供1100 nF/mm2的电容密度。高电容密度为高速计算的电源效率提供了巨大优势。

而新一代eDTC技术的的电容密度在电压应力后约为1100 nF/mm²,它比第一代eDTC高出3倍,比极板电容(MiM)电容高出50多倍。LSI芯片中集成的eDTC出色的电气特性为CoWoS-L带来了出色的信号完整性和电源完整性性能。

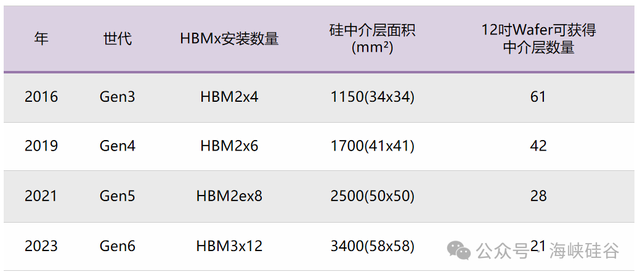

由于先进制程放缓,将多个逻辑芯片置于同一架构中成为了提升AI芯片性能的一种选择,另外HBM堆叠层数与配置数量也在持续增加,这两个因素都导致了对CoWoS封装中的Interposer面积的增加需求。

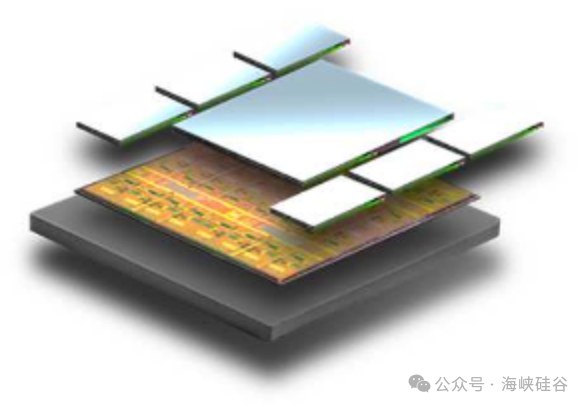

然而,CoWoS采用硅片作为基板与die之间的转接板,一般认为silicon interposer多采用早期的工艺制程,如60nm,90nm等等。其可提供两个维度的互联:1. 水平方向上die to die 高密度连接,这部分通常用于高带宽的数据传输。2. 垂直方向上,经过硅通孔(TSV)连至封装基板,这部分是晶片到外部世界的接口包括电源和GND。

顶端的die通过micro bump(典型pitch~40um)与interposer键合,而interposer与基板之间则通过常规的bump(典型pitch~130um)相连。目前Silcon Interposer一般可提供6层金属互联,最小线宽线距可做到0.4um/0.4um。考虑到线上寄生电阻对高速信号的影响,实际设计中常用更宽的metal option,例如0.8um甚至2.0um。

因此,Silicon Interposer存在两个挑战:

1)Interposer与下方基板之间的CTE (Coefficient of Thermal Expansion) 有较大差异,即不同温度下interposer与substrate存在膨胀比例差异。这种现象会带来CPI(Chip-to-Package Interaction)问题,降低系统的长期可靠性。

2)Interposer大小受限于掩膜版,虽然TSMC使用Mask Stitching等技术以扩大其尺寸,但终究有其局限性。

受制于以由于以上两个因素,目前CoWos-S可支持的最大尺寸约为2500平方毫米即三倍掩膜版尺寸,也就是Blackwell GPU上的两颗die+8xHBM的设计,再想增大面积恐怕不易。

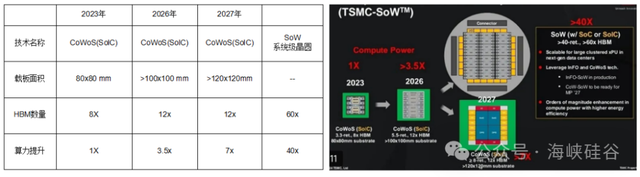

(2)CoWoS技术发展趋势由于CoWoS-S中介层面积进一步扩大、多芯片翘曲等带来的挑战,在CoWoS-S基础上再次迭代升级的难度正在大幅增加,因此,台积电正发力CoWoS-L技术。

CoWoS-L无需掩膜拼接,可以有效解决大型硅中介层良率问题,带来更高灵活性。CoWoS-L的中介层包括多个局部硅互连(local silicon interconnect,LSI)芯片和全局重布线(global redistribution layers),形成一个重组的中介层(reconstituted interposer,RI),以替代CoWoS-S中的单片硅中介层。LSI芯片保留了硅中介层的所有优秀特性,包括保留亚微米铜互连、硅通孔(TSV)和嵌入式深沟槽电容器(eDTC),以确保良好的系统性能,同时避免了单个大型硅中介层的良率损失问题。

另外,在RI中引入了绝缘体通孔(TIV)作为垂直互连,比TSV插入损耗更低。目前,台积电已成功实现具有3倍掩膜版尺寸的中介层的CoWoS-L结构,搭载多个SoC芯片和8个HBM,稳定的可靠性结果和卓越的电气性能表明,CoWoS-L架构有望延续CoWoS-S的扩展势头,以满足未来2.5D SiP系统在HPC和AI深度学习中的需求。

在电气性能方面,CoWoS平台引入第一代深沟槽电容器(eDTC)是用于提升电气性能。此前配备第一代eDTC的CoWoS可以将系统电源分配网络(PDN)的阻抗降低93%,压降比没有使用eDTC的情况低72%。此外,HBM VDDQ的同步开关噪声(SSN)可以在3.2 GHz时比没有eDTC的情况减少到38%。由于SSN减少,信号完整性也可以得到改善。CoWoS平台配合eDTC有利于电源完整性和信号完整性。新一代的eDTC可以提供1100 nF/mm²的电容密度。高电容密度为高速计算的电源效率提供了巨大的优势。出于良率考虑,单个硅芯片上eDTC的最大面积上限约为300平方毫米。通过连接所有LSI芯片的电容,CoWoS-L搭载多个LSI芯片,可以显著增加RI上的总eDTC电容。

因此,CoWos-L将成为下一阶段的主要封装类型。

另外,采用CoWoS技术的芯片堆栈版本,预计于2027年准备就绪,即CoWoS技术整合SoIC、HBM及其他元件,进而打造一个强大且运算能力媲美资料中心服务器机架,或甚至整台服务器的晶圆级系统。2027年后,3D版的CoWoS技术将登上历史舞台。

5、FOPLP 封装技术

由于CoWoS产能的紧缺,业内积极探索可替代的封装技术。近日,有消息传出,AI芯片龙头英伟达最快将于2026年导入扇出型面板级封装,借此缓解CoWoS先进封装产能吃紧,导致AI芯片供应不足的问题,英特尔、AMD等半导体大厂后续也将逐步加入扇出型面板级封装的阵营。

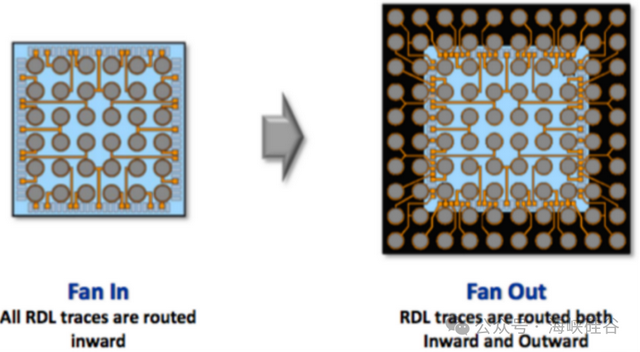

扇出型板级封装FOPLP,所谓的扇出(fan-out)是相对于扇入(fan-in)来说的,其封装的RDL线路和引脚不仅在芯片所处的投影面积之内,而且在投影面积的外围也有分布。面板级封装(PLP,panel level package),则是相对于晶圆级封装(WLP,wafer level package)来说的,就是之前采用晶圆作为载板的封装改为采用面板作为封装的载板。这些载板的材质可以选择金属、玻璃和高分子聚合物材料。

FOPLP技术是基于重新布线层(RDL)工艺,将芯片重新分布在大面板上进行互连的先进封装技术,能够将多个芯片、无源元件和互连集成在一个封装内。因此,扇出型板级封装的高面积利用率有效减少了浪费,同时能够在一次封装过程中处理更多的芯片,显著提高了封装效率,形成强大的规模效应,从而具有极强的成本优势。

据Yole的报告显示,FOWLP(扇出型晶圆级封装)技术的面积使用率<85%,FOPLP面积使用率>95%,这使得300mmx300mm的面板比同尺寸12英寸的晶圆可以多容纳1.64倍的die,这导致生产过程中生产速率的差异。

另外,CoWoS技术正式由于其结构特点,可以实现卓越的I/O密度和电气性能,因而成为AI算力芯片的首选。在这方面,FOPLP技术恰恰可以通过RDL工艺,实现高带宽、高密度的D2D互连,可以有效满足数据传输与处理的迫切需求。

因此,虽然FOPLP技术规格比台积电的CoWoS弱,但是由于工艺尺寸较大,在降低成本和突破产能方面具有潜在优势。

(未完待续)